В классической фон-неймановской ВМ функция арифметической и логической обработки данных возлагается на арифметико-логическое устройство (АЛУ). Учитывая разнообразие выполняемых операций и типов обрабатываемых данных, реально можно говорить не о едином устройстве, а о комплексе специализированных операционных устройств (ОПУ), каждое из которых реализует определенное подмножество арифметических или логических операций, предусмотренных системой команд ВМ. С этих позиций следует выделить:

· ОПУ целочисленной арифметики;

· ОПУ для реализации логических операций;

· ОПУ десятичной арифметики;

· ОПУ для чисел с плавающей запятой.

На практике две первых группы обычно объединяются в рамках одного операционного устройства. Специализированные ОПУ десятичной арифметики в современных ВМ встречаются достаточно редко, поскольку обработку чисел, представленных в двоично-десятичной форме, можно достаточно эффективно организовать на базе средств целочисленной двоичной арифметики. Таким образом, будем считать, что АЛУ образуют два вида операционных устройств: целочисленное ОПУ и ОПУ для обработки чисел в формате с плавающей запятой (ПЗ).

В минимальном варианте АЛУ должно содержать аппаратуру для реализации лишь основных логических операций, сдвигов, а также сложения и вычитания чисел в форме с фиксированной запятой (ФЗ). Опираясь на этот набор, можно программным способом обеспечить выполнение остальных арифметических и логических операций как для чисел с фиксированной запятой, так и для других форм представления информации. Следует, однако, учитывать, что подобный вариант не позволяет добиться высокой скорости вычислений, поэтому по мере расширения технологических возможностей доля аппаратных средств в составе АЛУ постоянно возрастает.

Рис. 1. Динамика изменения соотношения между аппаратной и программной реализациями функций АЛУ

На рис. 1 показана динамика изменения соотношения между аппаратной и программной реализациями функций АЛУ по мере развития элементной базы вычислительной техники. Здесь подразумевается, что по вертикальной оси откладывается календарное время.

Набор элементов, на основе которых строятся структуры различных ОПУ, называется структурным базисом. Структурный базис ОПУ включает в себя:

· регистры, обеспечивающие кратковременное хранение слов данных;

· управляемые шины, предназначенные для передачи слов данных;

· комбинационные схемы, реализующие вычисление функций микроопераций и логических условий по управляющим сигналам от устройства управления.

Одним из подходов к синтезу ОПУ является реализация каждой из операций в виде независимого блока (блок сложения, блок умножения, блок логических операций и т.п.). Такая структура имеет максимальную производительность по сравнению с другими вариантами структур, однако по затратам оборудования является избыточной. С практических позиций больший интерес представляют два иных вида структур ОПУ: жесткая и магистральная.

В ОПУ с жесткой структурой комбинационные схемы жестко распределены между всеми регистрами. К каждому регистру относится свой набор комбинационных схем, позволяющих реализовать определенные микрооперации. Достоинством ОПУ с жесткой структурой является высокое быстродействие, недостатком — малая регулярность структуры, что затрудняет реализацию таких ОПУ в виде больших интегральных схем.

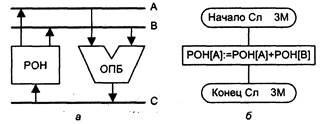

В ОПУ с магистральной структурой все внутренние регистры объединены в отдельный узел регистров общего назначения (РОН), а все комбинационные схемы — в операционный блок (ОПБ), который зачастую и ассоциируют с термином «арифметико-логическое устройство».

Операционный блок и узел регистров сообщаются между собой с помощью магистралей — отсюда и название «магистральное ОПУ».

Пример магистрального ОПУ представлен на рис. 2.

Рис. 2. Магистральное операционное устройство

В состав узла РОН здесь входят N регистров общего назначения, подключаемых к магистралям А и В через мультиплексоры MUX А и MUX В. Каждый из мультиплексоров является управляемым коммутатором, соединяющим выход одного из РОН с соответствующей магистралью. Номер подключаемого регистра определяется адресом а или b, подаваемым на адресные входы мультиплексора из устройства управления.

В операционных устройствах для обработки чисел с плавающей запятой вместо РОН часто используется отдельный узел регистров с плавающей запятой. По магистралям А и В операнды поступают на входы операционного блока, к которым подключается комбинационная схема, реализующая требуемую микрооперацию (по сигналу управления из УУ). Таким образом, любая микрооперация ОПБ может быть выполнена над содержимым любых регистров ОПУ. Результат микрооперации по магистрали С заносится через демультиплексор DMX С в конкретный регистр узла РОН. Демультиплексор представляет собой управляемый коммутатор, имеющий один информационный вход и N информационных выходов. Вход подключается к выходу с заданным адресом с, который поступает на адресные входы DMX С из УУ. Основным достоинством магистральных ОПУ является высокая универсальность и регулярность структуры, что облегчает их реализацию на кристаллах ИС. Магистральная структура ОПУ в современных ВМ является превалирующей.

Магистральные ОПУ классифицируют по виду и количеству магистралей, организации узла РОН, типу ОПБ. Магистрали ОПУ могут быть однонаправленными и двунаправленными, соответственно обеспечивающими передачу данных в одном или двух различных направлениях. Типичным режимом работы магистрали является разделение времени, при котором магистраль используется для передачи функционально разнотипных данных в различные моменты времени.

По функциональному назначению выделяют:

· магистрали внешних связей, соединяющих ОПУ с памятью и каналами ввода/ вывода ВМ;

· внутренние магистрали ОПУ, отвечающие за связь между узлом РОН и операционным блоком.

Количество магистралей зависит от архитектуры конкретной ВМ и обычно не превышает двух для внешних связей и трех — для внутренних.

Структура трехмагистрального ОПУ представлена на рис. 3, а, а соответствующая ему микропрограмма выполнения операции типа «сложение» — на рис. 3, б.

Рис. 3. Трехмагистральное ОПУ: а — структура; б — микропрограмма сложения

Данный вариант характеризуется наибольшим быстродействием: выборка операндов из РОН, выполнение микрооперации суммирования и запись результата в РОН — все эти действия производятся за один такт. Основной недостаток трехмагистральной организации — большая площадь, занимаемая магистралями на кристалле БИС (от 0,16 до 0,22 от площади кристалла).

Двухмагистральная организация при меньшей площади, покрываемой магистралями (от 0,06 до 0,19 от площади кристалла), требует введения как минимум одного буферного регистра (БР), предназначенного для временного хранения одного из операндов (рис. 4, a), при этом операция сложения будет выполняться уже за два такта (рис. 4, б):

Рис. 4. Двухмагистральное ОПУ: а — структура; б — микропрограмма сложения

Количество регистров в узле РОН магистрального ОПУ обычно превышает тот минимум, который необходим для реализации универсальной системы операций. Избыток регистров используется:

· для хранения составных частей адреса (индекса, базы);

· в качестве буферной, сверхоперативной памяти для повышения производительности ВМ за счет уменьшения требуемых пересылок между основной памятью и ОПУ.

Количество регистров колеблется в среднем от 8 до 16, иногда может достигать 32-64. В процессорах с сокращенным набором команд количество РОН доходит до нескольких сотен. Организация узла РОН может обеспечивать одноканальный или двухканальный доступ как по входу (записи), так и по выходу (считыванию). В первом случае к входу узла подключается один демультиплексор, а к выходу — один мультиплексор. Во втором случае доступ осуществляется с помощью двух демультиплексоров и (или) двух мультиплексоров. Двухканальный доступ повышает быстродействие ОПУ, так как позволяет обратиться параллельно к двум регистрам.

Рис. 5. Обобщенная схема операционного блока

Обобщенная схема ОПБ приведена на рис. 5. В нее входят: дешифратор микрокоманды ДшМК, формирователи кодов ФК1 и ФК2, многофункциональный сумматор См, сдвигатель Сдв и формирователь логических условий (ЛУ).

Дешифратор микрокоманды вырабатывает внутренние сигналы управления для элементов ОПБ. Он введен в схему с целью минимизации количества связей, требуемых для передачи сигналов управления из УУ.

Формирователи, кодов ФК1 и ФК2 служат для формирования прямых и инверсных кодов операндов, поступающих по магистралям А и В.

Многофункциональный сумматор выполняет микрооперации арифметического сложения (с учетом переноса СIN), сложения по модулю два, логического сложения и логического умножения кодов на левом и правом входах.

Формирователь логических условий на основе анализа кода на выходе См вырабатывает значения ознакомительных сигналов, передаваемых в УУ машины. Осведомительными сигналами могут быть: признак знака S, признак переполнения V, признак нулевого значения результата Z и т. п.

Сдвигатель служит для выполнения микроопераций сдвига кода на выходе См.