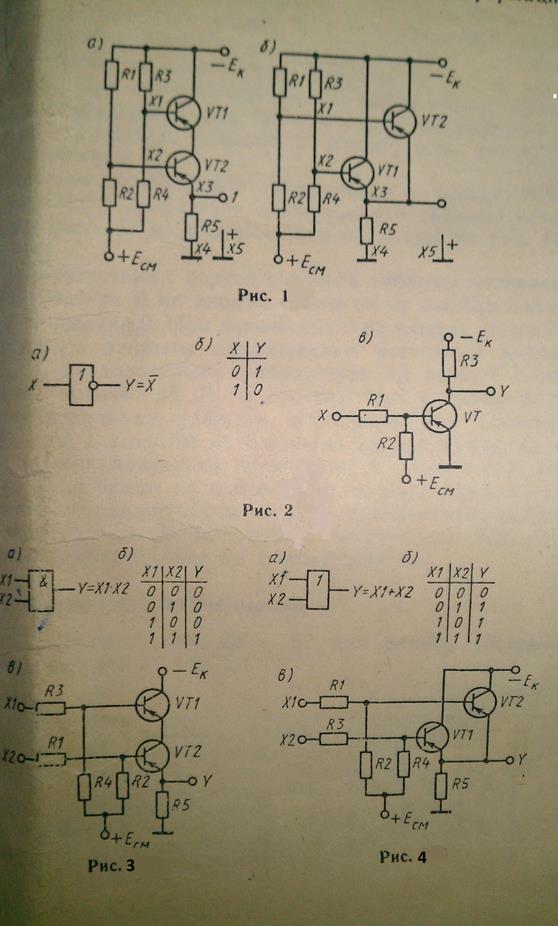

Цель работы: Изучение принципа действия логических схем И и Или на транзисторах и экспериментально подтверждение их таблиц истинности; наблюдение работы схемы И при передаче импульсной последовательности (рис.1, а, б).

Пояснение. В вычислительной технике для выполнения большинства операций используется двоичная система счисления, имеющая всего две значащие цифры 0 и 1, которые могут быть представлены разными уровнями потенциала. Например, 0 можно представить как отсутствие потенциала (нулевой потенциал на выходе или входе схемы либо настолько низкий потенциал, что им можно пренебречь), а 1 – как потенциал высокого уровня. Такая форма представления сигналов информации, называемая также цифровой, позволяет наиболее экономно и быстро их обрабатывать.

Для построения схем цифровой техники используют алгебру логики, основными операциями которой являются:

логическое отрицание (инверсия) Y= X (HE);

логическое умножение (конъюнкция) Y= X1*X2 (И);

логическое сложение (дизъюнкция) Y= X1+X2 (ИЛИ);

Наиболее полно и наглядно логическая функция представляется таблицей истинности (или состояний), в которой для каждой возможной операции входных логических переменных Х1, Х2, … указывается значение функции Y. Таблица истинности однозначно определяет алгоритм работы цифровой схемы. Создание логической схемы обычно начинают с составления таблицы истинности.

Условное графическое обозначение элемента HE, реализующего логическое отрицание, его таблица истинности и одна из возможны схем показаны на рис. 2, а – в. При логическом 0 на входе элемента на его выходе должна появиться логическая 1, а при логической 1 на входе будет логический 0.

При соединении входного зажима схемы с корпусом на базу транзистора от источника питания + Есм подаётся положительный потенциал. При этом транзистор VTзакрывается и напряжение на его коллекторе увеличивается до напряжения источника Ек, т.е. на выходе схемы появляется логическая 1. При соединение входного зажима схемы с источником питания Ек (на входе схемы логическая 1) транзистор переходит в насыщение и напряжение на его коллекторе уменьшается до долей вольт, что соответствует появлению на выходе логического 0.

Такую схему называют инвертором. В ней используют свойство каскада на транзисторе, включенном с ОЭ, изменять фазу входного сигнала на 1800, т.е. инвертировать его.

Условное графическое обозначение элемента И, реализующего логическое умножение, его таблица истинности и одна из возможных схем показаны на рис. 3, а – в.

Первая строка таблицы истинности показывает, что при логическом 0 на входах схемы (Х1=0 и Х2=0) на её выходе также будет логический 0. При логических 0 входах схемы оба транзистора закрыты положительным напряжением +Есм. Напряжение на выходе близко к нулю, так как ток через резистор R5 равен нулю. В соответствии с второй и третьей строчками таблицы истинности при логической 1 только на одном из входов схемы на её выходе должен быть логический 0. Входной сигнал, соответствующий логической 1, открывает транзистор, на базу которого он поступает, второй транзистор остаётся закрытым и на входе схемы при этом сохраняется логический 0. В соответствии с четвёртой строчкой таблицы истинности логические 1 на обоих входах схемы вызывают появление на её выходе логической 1. При поступлении на оба входа схемы логической 1 открываются оба транзистора и напряжение на выходе становится близким к напряжению источника Ек (логическая 1).

Условное графическое обозначение элемента ИЛИ, реализующего логическое сложение, его таблица истинности и одна из возможных схем показаны на рис. 4, а – в.

В соответствии с первой строчкой таблицы истинности при логических 0 на входах схемы её выходе должен быть логический 0. При логических 0 на входах схемы оба транзистора закрыты напряжением источника питания +Есм и, следовательно, напряжение источника питания к нулю (логический 0). В соответствии с тремя следующими строчками таблицы истинности при появлении логической 1 хотя бы на одном из входов схемы на выходе должна появиться логическая 1. Появление логической 1 на одном из входов или на двух входах одновременно открывает один или оба транзистора, вследствие чего на выходе появляется напряжение, близкое к напряжению источника Ек (логическая 1).

Порядок выполнения работы:

1.Вычертить табл. 1 и 2 для записи состояний логических схем И и Или.

| Выводы | Х1 | Логическое состояние Напряжения, В | |||||||

| Х2 | Логическое состояние Напряжения, В | ||||||||

| Выход | Y | Логическое состояние Напряжения, В | |||||||

Таблица 1

Таблица 2

| Выводы | Х1 | Логическое состояние Напряжения, В | |||||||

| Х2 | Логическое состояние Напряжения, В | ||||||||

| Выход | Y | Логическое состояние Напряжения, В | |||||||

2. Зарисовать электрические схемы логических элементов И и Или (см. рис. 1 а, б).

3. Собрать схему И, пользуясь графическими обозначениями на сменной панели 87Л-01/32. (см рис. 1, а), и исследовать её, подавая на входы сигналы в соответствии с табл. 1. Измерить напряжение на входах и выходе схемы и занести в табл. 1.

4. Наблюдать прохождение на выход схемы И импульсной последовательности, подаваемой на один из её входов при логической 1 на другом входе.

5. Собрать схему Или, пользуясь графическими обозначениями на сменной панели 87Л-01/32 (см. рис. 1, б), и исследовать её, подавая на входы сигналы в соответствии табл. 2. Измерить напряжения на входах и выходе схемы и занести результаты в табл. 2.

Методические указания:

1. При сборке схемы И используют: R1= 15 кОм, R2=R4=12 кОм, R3=12 кОм, R5=1 кОм; VT1 иVT2– транзисторы КТ361А.

2. При сборке схемы Или используют: R1=R3=12 кОм, R2=R4=33 кОм, R5=2 кОм; VT1 иVT2– транзисторы КТ361А.

3. Устанавливают на выходе ГН2 напряжение 12В, которое измеряют ИВ стенда, для чего его переключатель переводят в положение <<ГН2 25В>>. Зажим ГН2 <<–>> подключают к гнезду <<–Ек>> исследуемой схемы, а зажим <<+>> – к гнезду Х5.

4. Поворачивают регуляторы ГН1<<Грубо>> и <<Точно>> до упора по часовой стрелке, при этом выходное напряжение ГН1 составляет 0,5–0,7 В. В зажим ГН1 <<+>> подключают к гнезду <<+Есм>>, а зажим <<–>> – к гнезду Х4.

5. Необходимо учитывать, что для подачи входы схемы И логической 1 включают резисторы R1 и R3, при их отключении на входы схемы поступают логические 0.

6. Для измерения напряжений в схеме используют АВМ1 на пределах измерения <<25В>>, <<10В>>, <<5В>>, <<2,5В>>, <<1В>>. Напряжения измеряют в гнёздах Х1,Х2,Х3. При подключении измерительных приборов следует помнить, что гнёзда Х4 и Х5 обеих схем соединены между собой внутренним монтажом.

7. Переводят переключатели Г3Ч и ГПИ <<Диапазон>> ГПИ <<Амплитуда>> максимальную амплитуду выходных импульсов. Зажим ГПИ <<>> соединяют с входом Х1 (гнездо Х1) или Х2 (гнездо Х2) соответственно при отключённых резисторах R1 и R3.

8. Для наблюдения выходного сигнала вход осциллографа подключают к гнезду 1 схемы И, а вывод <<>> – к свободному гнезду Х4 или Х5 схемы ИЛИ.

9. При исследовании схемы ИЛИ следуют указаниям, приведённым для исследования схемы И (кроме п. 7 и 8).

Контрольные вопросы:

1. Почему в вычислительной техники используют двоичную систему счисления?

2. Как работают схемы НЕ, И и ИЛИ?

3. Составьте схему ИЛИ–НЕ и заполните её таблицу истинности.

4. Составьте схему И–НЕ и заполните таблицу истинности для этой схемы.