ЛАБОРАТОРНАЯ РАБОТА № 15

ИЗУЧЕНИЕ ВЛИЯНИЯ СТЕК-РАСПОЛОЖЕНИЯ ТРАНЗИСТОРОВ НА ПАРАМЕТРЫСХЕМЫ.

| Цель работы: | изучение характеристик и параметров КМОП логики, содержащей стек структуры. |

| Оборудование: | Вычислительные мощности УНЦ Synopsys |

| Продолжительность работы: 4 часа. |

ТЕОРЕТИЧЕСКИЕ СВЕДЕНИЯ

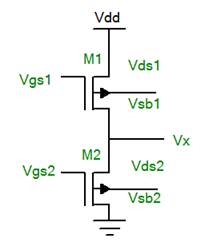

Впервые стек-расположение транзисторов и их воздействие на схему было проанализировано относительно подпорогового тока утечки. Было замечено, что в случае последовательно соединённых транзисторов, напряжение Vgs у транзистора, который находится выше в стеке, имеет более низкое значение. Кроме того, пороговое напряжение верхних транзисторов увеличивается из-за того, что создаётся отрицательное напряжение исток-подложка Vsb1. В результате стек структура из отключенных транзисторов потребляет статической мощности меньше, чем отдельный транзистор в стеке.

Рисунок 1. Стек из транзисторов

Для отключённого транзистора, показанного на рисунке 1, ток утечки ( ) может быть описан следующим выражением:

) может быть описан следующим выражением:

где  , n - коэффициент крутизны,

, n - коэффициент крутизны,  - температурное напряжение (потенциал)

- температурное напряжение (потенциал)  ,

,  - напряжение затвор-исток,

- напряжение затвор-исток,  - пороговое напряжение при нулевом напряжении на подложке,

- пороговое напряжение при нулевом напряжении на подложке,  - напряжение исток-подложка,

- напряжение исток-подложка,  - напряжение сток-исток,

- напряжение сток-исток,  - коэффициент влияния подложки,

- коэффициент влияния подложки,  - DIBL коэффициент,

- DIBL коэффициент,  - подвижность при нулевом напряжении на подложке,

- подвижность при нулевом напряжении на подложке,  - емкость затвора,

- емкость затвора,  - ширина транзистора,

- ширина транзистора,  - эффективная ширина канала.

- эффективная ширина канала.

Давайте предположим, что два транзистора M1 и М2, которые составляют стек-структуру (рисунок 2), отключены. Предположим также, что ширина транзисторов М1 и М2 одинаковая, т.е W(M1) = W(M2). Тогда токи транзисторов  и

и  могут быть описаны так:

могут быть описаны так:

|

|

где  - напряжение в точке соединения транзисторов.

- напряжение в точке соединения транзисторов.

Теперь вычислим уменьшение тока утечки между  и

и  . Коэффициент уменьшения утечки может быть описан как:

. Коэффициент уменьшения утечки может быть описан как:

в выражении (4) можно вычислить полагая, что

в выражении (4) можно вычислить полагая, что  =

=  , и решив следующее выражение:

, и решив следующее выражение:

Если все параметры известны, то мы можем рассчитать уменьшение тока утечки, вызванное стек-эффектом, используя выражение (4) и (5).

Из выражения (5) сначала мы рассчитаем Vx, а потом с помощью выражения (4) получим коэффициент уменьшения утечки Х.

Таблица1. Параметры модели для утечки

| Параметр | Значение |

| Vdd | 1В |

| Vth | 0.397В |

| n (коэффициент подпороговой крутизны) | 1,7 |

| η (DIDL коэффициент) | 0.0074В/В |

| γ (коэффициент влияния подложки) | 0,4B/B |

Нужно отметить, что коэффициент уменьшения утечки увеличивается при уменьшении топологических размеров, потому что коэффициент η при этом также увеличивается.

ЛАБОРАТОРНОЕ ЗАДАНИЕ

а) Изучение параметров и характеристик логического элемента NAND 2

Создайте в схемотехническом редакторе элемент NAND 2, как показано на рисунке 2.

Рисунок 2. Элемент NAND 2

По указанию преподавателя задайте требуемые входные воздействия, выходную ёмкость.

Рассчитайте времена фронтов выходных сигналов и задержку прохождения сигналов при различных комбинациях входных значений. В качестве примера можно использовать следующее spice описание:

*NAND2 Gate

*Propagation Delay, Transition Time

***Spice model

.lib "SAED90nm.lib" 'TT_12'

***********************************

***Netlist

mg_pmos4t1 out ina vdd vdd p12 L=0.1u W=0.7u

mg_pmos4t2 out inb vdd vdd p12 L=0.1u W=0.7u

mg_pmos4t3 out ina N00513 0 n12 L=0.1u W=0.27u

mg_pmos4t4 N00513 inb 0 0 n12 L=0.1u W=0.27u

|

|

***********************************

***Parameters

.param tr=TR_val

.param freq = FREQ_val

.param per = '1/freq'

.param vdd = VDD_val

.param tst = '0.5*per'

.param pw = '0.5*per-tr'

.param Temp = Temp_val

.param LOAD = LOAD_val

**********************************

***Supply Voltage

vvdd vdd 0 vdd

vvss vss 0 0

**********************************

***Temperature

.temp Temp

**********************************

***Input Signals

vina ina 0 pulse (vdd 0 'tst+0*per' tr tr pw '2*per')

vinb inb 0 pulse (vdd 0 'tst+1*per' tr tr pw '2*per')

**********************************

***Load

cload out 0 LOAD

**********************************

***Measures

***Propagation Delay

.measure tran tplh_ina_out trig v(ina) val='0.5*vdd' fall=1 targ v(out) val='0.5*vdd' rise=1

.measure tran tphl_ina_out trig v(ina) val='0.5*vdd' rise=1 targ v(out) val='0.5*vdd' fall=1

.measure tran tplh_inb_out trig v(inb) val='0.5*vdd' fall=1 targ v(out) val='0.5*vdd' rise=2

.meas tran tphl_inb_out trig v(inb) val='0.5*vdd' rise=1 targ v(out) val='0.5*vdd' fall=2

***Transition Time

.meas tran ttlh_ina_out trig v(out) val='0.1*vdd' rise=1 targ v(out) val='0.9*vdd' rise=1

.meas tran tthl_ina_out trig v(out) val='0.9*vdd' fall=1 targ v(out) val='0.1*vdd' fall=1

.meas tran ttlh_inb_out trig v(out) val='0.1*vdd' rise=2 targ v(out) val='0.9*vdd' rise=2

.meas tran tthl_inb_out trig v(out) val='0.9*vdd' fall=2 targ v(out) val='0.1*vdd' fall=2

***Dynamic Power

.meas tran dynamic avg P(vvdd) from '1*per' to '5*per'

***********************************

***Options

.option post

.option probe

***********************************

.probe v(*)

***********************************

***Analysis

.tran '0.01*tr' '5*per'

***********************************

.end

Рассчитайте статическую мощность утечки при различных комбинациях входных значений. В качестве примера можно использовать следующее spice описание:

*NAND2 Gate

*Leakage current

***Spice model

.lib "SAED90nm.lib" 'TT_12'

***********************************

***Netlist

mg_pmos4t1 out ina vdd vdd p12 L=0.1u W=0.7u

mg_pmos4t2 out inb vdd vdd p12 L=0.1u W=0.7u

mg_pmos4t3 out ina N00513 0 n12 L=0.1u W=0.27u

mg_pmos4t4 N00513 inb 0 0 n12 L=0.1u W=0.27u

***********************************

***Parameters

.param tr=TR_val

.param freq = FREQ_val

.param per = '1/freq'

.param vdd = VDD_val

.param tst = '0.5*per'

.param pw = '0.5*per-tr'

.param Temp = Temp_val

.param LOAD = LOAD_val

**********************************

***Supply Voltage

vvdd vdd 0 vdd

vvss vss 0 0

**********************************

|

|

***Temperature

.temp Temp

**********************************

***Input Signals

***Input Signals

vina ina 0 pwl (0 0 'per' 0 'per+tr' vdd '10*per' vdd)

vinb inb 0 pwl (0 0 'pw' 0 'pw+tr' vdd 'per' vdd 'per+tr' 0 'per+pw' 0 'per+pw+tr' vdd '10*per' vdd)

**********************************

***Load

cload out 0 LOAD

**********************************

***Measures

***Leakage Power

.meas tran Ileak00 find I(vvdd) at='pw/2'

.meas tran Ileak01 find I(vvdd) at='1.5*pw'

.meas tran Ileak10 find I(vvdd) at='2.5*pw'

.meas tran Ileak11 find I(vvdd) at='3.5*pw'

.meas tran Pleak00 param='Ileak00*vdd'

.meas tran Pleak01 param='Ileak01*vdd'

.meas tran Pleak10 param='Ileak10*vdd'

.meas tran Pleak11 param='Ileak11*vdd'

***********************************

***Options

.option post

.option probe

***********************************

.probe v(*)

***********************************

***Analysis

.tran '0.01*tr' '5*per'

***********************************

.end