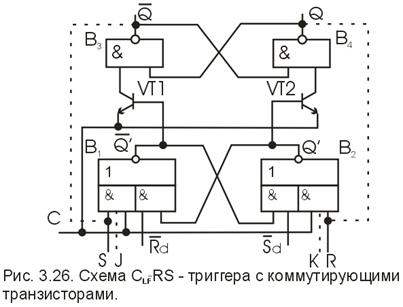

В таких триггерах организация блокировки передачи информации из триггера М в триггер S во время действия ТИ осуществляется за счет дополнительных блокирующих транзисторов, включенных между основным и вспомогательным триггерами. Схемная реализация такого триггера приведена на рис. 7.

|

В отсутствие ТИ (С=0) открыт один из двух блокирующих транзисторов VT1 или VT2 и притом тот, на базе которого действует уровень 1. Предположим, что триггер М находится в состоянии  `=1,

`=1,  `=0. В этом случае открыт транзистор VT2, то есть на его коллекторе низкий уровень и, следовательно, на выходе элемента В4 действует уровень 1 (

`=0. В этом случае открыт транзистор VT2, то есть на его коллекторе низкий уровень и, следовательно, на выходе элемента В4 действует уровень 1 ( =1), а на выходе В3 — уровень 0 (

=1), а на выходе В3 — уровень 0 ( =0). При поступлении ТИ (С=1) оба транзистора оказываются закрытыми высоким уровнем сигнала, действующим на их эмиттерах, и тем самым обеспечивается сохранность информации триггером S и блокировка приема информации от триггера М, в который в это же время производится запись информации. По окончании ТИ (С=0) блокировка снимается, то есть на эмиттерных входах обоих транзисторов действуют уровни 0 и осуществляется передача состояния триггера М в триггер S. При этом триггер S устанавливается в новое состояние через переходное состояние

=0). При поступлении ТИ (С=1) оба транзистора оказываются закрытыми высоким уровнем сигнала, действующим на их эмиттерах, и тем самым обеспечивается сохранность информации триггером S и блокировка приема информации от триггера М, в который в это же время производится запись информации. По окончании ТИ (С=0) блокировка снимается, то есть на эмиттерных входах обоих транзисторов действуют уровни 0 и осуществляется передача состояния триггера М в триггер S. При этом триггер S устанавливается в новое состояние через переходное состояние  =

=  =1.

=1.

Организация  и

и  триггеров на базе данного триггера показана на рис. 7 штриховыми линиями.

триггеров на базе данного триггера показана на рис. 7 штриховыми линиями.

Резюме: кроме рассмотренных, возможны и другие схемотехнические приемы организации блокировки в М-S-триггерах. Однако приведенные схемные решения получили наибольшее распространение в силу их высоких схемотехнических и функциональных возможностей.

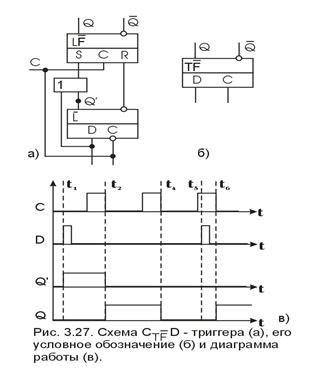

Из других разновидностей триггеров с различными способами управления записью рассмотрим

Триггеры с управлением записью видов  ,

,

Данные триггеры существуют только в тактируемом варианте и работают по следующему алгоритму: в отсутствие и во время действия ТИ информация принимается и запоминается внутренней памятью схемы управления. Другими словами, такие триггеры принимают информацию в течение всей длительности периода, а фиксируют по срезу ТИ. В дальнейшем эти триггеры будем называть триггерами вида  , где Т — период следования ТИ. Возможны два варианта таких триггеров

, где Т — период следования ТИ. Возможны два варианта таких триггеров  и

и  . Особенности их работы рассмотрим на примере

. Особенности их работы рассмотрим на примере  триггера, схема которого приведена на рис. 8.

триггера, схема которого приведена на рис. 8.

|

Она включает в себя триггеры  ,

,  и элемент ИЛИ. Работа триггера иллюстрируется диаграммой (рис. 8, в). В момент t1 на вход D поступает сигнал с уровнем 1, и так как

и элемент ИЛИ. Работа триггера иллюстрируется диаграммой (рис. 8, в). В момент t1 на вход D поступает сигнал с уровнем 1, и так как  триггер принимает информацию по уровню

триггер принимает информацию по уровню  , то в момент t1 триггер установится в состояние

, то в момент t1 триггер установится в состояние  `=1. После окончания ТИ (момент t2) состояние Q=1 зафиксируется и на выходе триггера. Одновременно в момент t2 на входе D установится уровень 0 и

`=1. После окончания ТИ (момент t2) состояние Q=1 зафиксируется и на выходе триггера. Одновременно в момент t2 на входе D установится уровень 0 и  триггер примет нулевое состояние (Q`=0).

триггер примет нулевое состояние (Q`=0).

К некоторому моменту t3  триггер будет находиться в состоянии 0 и, следовательно, в момент t4 это состояние зафиксируется и на выходе

триггер будет находиться в состоянии 0 и, следовательно, в момент t4 это состояние зафиксируется и на выходе  триггера (Q=0). В момент t5 вновь поступает сигнал D=1. Но теперь

триггера (Q=0). В момент t5 вновь поступает сигнал D=1. Но теперь  триггер не принимает эту информацию. В итоге состояние D=1 через элемент ИЛИ поступает на вход S

триггер не принимает эту информацию. В итоге состояние D=1 через элемент ИЛИ поступает на вход S  триггера и фиксируется на его выходах после окончания ТИ (момент t6).

триггера и фиксируется на его выходах после окончания ТИ (момент t6).

В интегральной схемотехнике применяются в основном  триггеры, хотя в практике возможны и другие их функциональные типы, например

триггеры, хотя в практике возможны и другие их функциональные типы, например  триггеры.

триггеры.

ЛИТЕРАТУРА

1. Новиков Ю.В. Основы цифровой схемотехники. Базовые элементы и схемы. Методы проектирования. М.: Мир, 2001. - 379 с.

2. Новиков Ю.В., Скоробогатов П.К. Основы микропроцессорной техники. Курс лекций. М.: ИНТУИТ.РУ, 2003. - 440 с.

3. Пухальский Г.И., Новосельцева Т.Я. Цифровые устройства: Учеб. пособие для ВТУЗов. СПб.: Политехника, 2006. - 885 с.

4. Преснухин Л.Н., Воробьев Н.В., Шишкевич А.А. Расчет элементов цифровых устройств. М.: Высш. шк., 2001. - 526 с.

5. Букреев И.Н., Горячев В.И., Мансуров Б.М. Микроэлектронные схемы цифровых устройств. М.: Радио и связь, 2000. - 416 с.

6. Соломатин Н.М. Логические элементы ЭВМ. М.: Высш. шк., 2000. - 160 с.