по дисциплине “Архитектура компьютера ”

| Студенту | Лесько Николаю Васильевичу | Группы | ИС-02а | |||

| (Фамилия, Имя, Отчество) | ||||||

| Тема проекта | Разработка структуры и эмулятора микро ЭВМ на базе | |||||

| гипотетического микропроцессора. | ||||||

| Исходные данные к проекту | Техническая информация о | |||||

| микропроцессоре МК51 и заданном наборе команд. | ||||||

| Перечень искомых результатов | Программа эмуляции выполнения | |||||

| заданных команд в разработанной микро-ЭВМ; разработанная структура | ||||||

| МП, микро ЭВМ, схема АЛУ и алгоритмов выполнения команд. | ||||||

| Рекомендуемая литература | В.В. Сташин А.В. Урусов “Проектирование | |||||

| цифровых устройств на однокристальных микроконтроллерах” | ||||||

| Дата выдачи задания | 04.10.2004 | ||||||||||||||||||||

| Дата защиты проекта | 20.12.2004 | ||||||||||||||||||||

| Руководитель | ассистент Мирошниченко Д.Ю. | ||||||||||||||||||||

| (подпись) | (должность, Ф. И. О) | ||||||||||||||||||||

| ассистент Патрушев В.А. | |||||||||||||||||||||

| (подпись) | (должность, Ф. И. О) | ||||||||||||||||||||

| Разработчик | ст. гр. ИС-02а Лесько Н.В. | ||||||||||||||||||||

| (подпись) | |||||||||||||||||||||

| РЕФЕРАТ Пояснительная записка: 46 с., рис. 22, 5 приложений, 4 источника. Основной целью создания проекта является изучение структуры микропроцессора МК51 и выполнение следующих работ по проектированию микропроцессора: разработка структуры АЛУ, алгоритмов выполнения команд, структуры гипотетического микропроцессора и структуры микро-ЭВМ. Система команд гипотетического микропроцессора является подмножеством системы команд микропроцессора МК51. Также целью данного проекта является создание программы эмуляции выполнения гипотетическим микропроцессором команд, составляющих его систему команд. Необходимо предусмотреть возможность просмотра алгоритма выполнения команд в автоматическом и пошаговом режимах. Предлагаемая программа эмуляции применима в учебных целях при изучении работы микропроцессора МК51, предназначена для студентов, изучающих курс: “ Архитектура компьютера”. МК51, АЛУ, БИС, МИКРОПРОЦЕССОР, МИКРОПРОГРАММА | |||||||||||||||||||||

| Д080404.1.02.02/008.КП | |||||||||||||||||||||

| Фамилия | Подпись | Дата | |||||||||||||||||||

| Разработал | Лесько Н.В. | Разработка структуры и эмулятора микро ЭВМ на базе гипотетического микропроцессора. | Литера | Лист | Листов | ||||||||||||||||

| Рук. Проекта | Вороной С.М. | У | |||||||||||||||||||

| Патрушев В.А | ДонГИИИ, каф. ТИ группа ИС-02а | ||||||||||||||||||||

| МирошниченкоД.Ю. | |||||||||||||||||||||

| Н. Контр. | Патрушев В.А | ||||||||||||||||||||

| Зав. Каф. | Вороной С.М. | ||||||||||||||||||||

СОДЕРЖАНИЕ

Введение ………………………………………………………………………….5

1. Анализ структуры микропроцессора-прототипа.…………………………....6

1.1 Структурная схема МК51……………………………………………………6

1.2 Арифметическо-логическое устройство……………………………………6

1.3 Резидентная память…………………………………………………………..7

1.4 Аккумулятор и ССП …………………………………………………………8

1.5 Регистры-указатели………………………………………………………….10

1.6 Таймер/счетчик………………………………………………………………10

1.7 Устройство управления и синхронизации ………………………………...10

2. Постановка задач проекта …………………………………………………...12

2.1 Требования к структуре гипотетического микропроцессора…………….12

2.2 Требования к структуре АЛУ микропроцессора………………………….13

2.3 Требования к структуре микро ЭВМ ……………………………………...13

3. Разработка арифметико-логического устройства…………………………..14

3.1 Структурные схемы ОА операций…………………………………………14

3.2 Структурная схема АЛУ……………………………………………..……..16

3.3 Микропрограммы работы АЛУ…………………………………………… 18

4. Разработка структуры микропроцессора…………………………………... 21

4.1 Разработка команд гипотетического микропроцессора…………………. 21

4.2 Структура гипотетического микропроцессора…………………………... 22

4.3 Организация оперативного запоминающего устройства………………....24

4.4 Организация резидентной памяти программ…………………………….. 24

4.5 Структура регистра команд……………………………………………… 25

4.6 Разработка микропрограмм выполнения команд………………………....26

5. Разработка Микро ЭВМ……………………………………………………...27

5.1 Разработка структуры микро ЭВМ………………………………………..27

5.2 Разработка структуры шин………………………………………………....27

5.3 Разработка структуры ОЗУ…………………………………………….….28

5.4 Управление выполнением команд…………………………………….….28

6. Разработка программы эмуляции микро ЭВМ………………………….…29

6.1 Структура эмулятора…………………………………………………….…29

6.2 Алгоритм функционирования эмулятора………………………………....29

Выводы……………………………………………………………………….…32

Список использованных источников………………………………………....33

Приложение А Техническое задание на микро ЭВМ………………………..34

Приложение Б Техническое задание на программу-эмулятор………………37

Приложении В Руководство пользователя………………………………….. 39

Приложение Г Экранные формы ……………………………………………..41

Приложение Д Листинг программы ………………………………………….43

СОДЕРЖАНИЕ

Введение ………………………………………………………………………….5

1. Анализ структуры микропроцессора-прототипа.…………………………....6

1.1 Структурная схема МК51……………………………………………………6

1.2 Арифметическо-логическое устройство……………………………………6

1.3 Резидентная память…………………………………………………………..7

1.4 Аккумулятор и ССП …………………………………………………………8

1.5 Регистры-указатели………………………………………………………….10

1.6 Таймер/счетчик………………………………………………………………10

1.7 Устройство управления и синхронизации ………………………………...10

2. Постановка задач проекта …………………………………………………...12

2.1 Требования к структуре гипотетического микропроцессора…………….12

2.2 Требования к структуре АЛУ микропроцессора………………………….13

2.3 Требования к структуре микро ЭВМ ……………………………………...13

3. Разработка арифметико-логического устройства…………………………..14

3.1 Структурные схемы ОА операций…………………………………………14

3.2 Структурная схема АЛУ……………………………………………..……..16

3.3 Микропрограммы работы АЛУ…………………………………………… 18

4. Разработка структуры микропроцессора…………………………………... 21

4.1 Разработка команд гипотетического микропроцессора…………………. 21

4.2 Структура гипотетического микропроцессора…………………………... 22

4.3 Организация оперативного запоминающего устройства………………....24

4.4 Организация резидентной памяти программ…………………………….. 24

4.5 Структура регистра команд……………………………………………… 25

4.6 Разработка микропрограмм выполнения команд………………………....26

5. Разработка Микро ЭВМ……………………………………………………...27

5.1 Разработка структуры микро ЭВМ………………………………………..27

5.2 Разработка структуры шин………………………………………………....27

5.3 Разработка структуры ОЗУ…………………………………………….….28

5.4 Управление выполнением команд…………………………………….….28

6. Разработка программы эмуляции микро ЭВМ………………………….…29

6.1 Структура эмулятора…………………………………………………….…29

6.2 Алгоритм функционирования эмулятора………………………………....29

Выводы……………………………………………………………………….…32

Список использованных источников………………………………………....33

Приложение А Техническое задание на микро ЭВМ………………………..34

Приложение Б Техническое задание на программу-эмулятор………………37

Приложении В Руководство пользователя………………………………….. 39

Приложение Г Экранные формы ……………………………………………..41

Приложение Д Листинг программы ………………………………………….43

| |||||||||||||||||||||

| Разработал | Фамилия | Подпись | Дата | Д080404.1.02.02/008.КП | Лист | ||||||||||||||||

| ст.гр.ИС-02а | Лесько Н.В. | ||||||||||||||||||||

ВВЕДЕНИЕ

Развитие микроэлектроники и широкое применение ее изделий в промышленном производстве, в устройствах и системах управления самыми разнообразными объектами и процессами является в настоящее время одним из основных направлений научно-технического прогресса.

Использование микроэлектронных средств в изделиях производственного и культурно-бытового назначения не только приводит к повышению технико-экономических показателей изделий, но и придает им принципиально новые потребительские качества.

Однокристальные МК представляют собой приборы, конструктивно выполненные в виде БИС и включающие в себя составные части «голой» микроЭВМ: микропроцессор, память программ и память данных, а также программируемые интерфейсные схемы для связи с внешней средой. Использование МК в системах управления обеспечивает достижение исключительно высоких показателей эффективности при столь низкой стоимости, что микроконтроллерам, видимо, нет разумной альтернативной элементной базы для построения управляющих или регулирующих систем.

Цель создания курсового проекта: исследовать структуру и алгоритмы выполнения заданного набора команд микропроцессора МК51 при заданном режиме адресации, разработать на его основе собственный гипотетический микропроцессор, выполняющий указанное подмножество команд и создать программу, позволяющую их эмулировать.

Таким образом, данный программный продукт применим в учебных целях при изучении работы МК51 для наглядной демонстрации алгоритмов выполнения его команд, и предназначен для студентов, изучающих курс: “Архитектура компьютера”.

1.1 Структурная схема МК51

Основу структурной схемы МК51 (рисунок 1.1z:\ALF\HTM\MK_4\struct_shema_mk51.htm - рис.3.2) образует внутренняя двунаправленная 8-битная шина, которая связывает между собой все основные узлы и устройства: резидентную память, АЛУ, блок регистров специальных функций, устройство управления и порты ввода/вывода. Рассмотрим основные элементы структуры и особенности организации вычислительного процесса в МК51.

Рисунок 1.1 – Структурная схема МК51

1.2 Арифметическо-логическое устройство

8-битное АЛУ может выполнять арифметические операции сложения, вычитания, умножения и деления; логические операции, а также операции циклического сдвига, сброса, инвертирования и т.п. В АЛУ имеются программно недоступные регистры T1 и T2 для временного хранения операндов, схема десятичной коррекции и схема формирования признаков.

Простейшая операция сложения используется в АЛУ для инкрементирования содержимого регистров, продвижения регистра-указателя данных и автоматического вычисления следующего адреса РПП. Простейшая операция вычитания используется в АЛУ для декрементирования регистров и сравнения переменных.

Простейшие операции автоматически образуют "тандемы" для выполнения в АЛУ таких операций, как, например, инкрементирование 16-битных регистровых пар. В АЛУ реализуется механизм каскадного выполнения простейших операций для реализации сложных команд. Так, например, при выполнении одной из команд условной передачи правления по результату сравнения в АЛУ трижды инкрементируется СК, дважды производится чтение из РПД, выполняется арифметическое сравнение двух переменных, формируется 16-битный адрес перехода и принимается решение о том, делать или не делать переход по программе. Все перечисленные операции выполняются в АЛУ всего лишь за 2 мкс.

Важной особенностью АЛУ является его способность оперировать не только байтами, но и битами. Отдельные программно-доступные биты могут быть установлены, сброшены, инвертированы, переданы, проверены и использованы в логических операциях. Эта способность АЛУ, оперировать битами, столь важна, что во многих описаниях МК51 говорится о наличии в нем "булевского процессора". Для управления объектами часто применяются алгоритмы, содержащие операции над входными и выходными булевскими переменными (истина/ложь), реализация которых средствами обычных микропроцессоров сопряжена с определенными трудностями.

Таким образом, АЛУ может оперировать четырьмя типами информационных объектов: булевскими (1 бит), цифровыми (4 бита), байтными (8 бит) и адресными (16 бит). В АЛУ выполняется 51 различная операция пересылки или преобразования этих данных. Так как используется 11 режимов адресации (7 для данных и 4 для адресов), то путем комбинирования "операция/ режим адресации" базовое число команд 111 расширяется до 255 из 256 возможных при однобайтном коде операции.

1.3 Резидентная память

Память программ и память данных, размещенные на кристалле МК5 физически и логически разделены, имеют различные механизмы адресации, работают под управлением различных сигналов и выполняют разные функции.

Резидентная память программ

Память программ (ПЗУ или СППЗУ) имеет емкость 4 Кбайта и предназначена для хранения команд, констант, управляющих слов инициализации, таблиц перекодировки входных и выходных сменных и т.п. РПП имеет 16-битную шину адреса, через которую обеспечивается доступ из счетчика команд или из регистра-указателя данных. Последний выполняет функции базового регистра при косвенных переходах по программе или используется в командах, оперирующих с таблицами.

Резидентная память данных

Память данных (ОЗУ) предназначена для хранения переменных в процессе выполнения прикладной программы, адресуется одним байтом и имеет емкость 128 байт. Кроме того, к адресному пространству РПД примыкают адреса регистров специальных функций (РСФ), которые перечислены в табл. 3.1.

Память программ, так же как и память данных, может быть расширена до 64 Кбайт путем подключения внешних БИС.

1.4 Аккумулятор и ССП

Аккумулятор и ССП. Аккумулятор является источником операнда и местом фиксации результата при выполнении арифметических, логических операций и ряда операций передачи данных. Кроме того, только с использованием аккумулятора могут быть выполнены операции сдвигов, проверка на нуль, формирование флага паритета и т.п.

Таблица 1.1 – Блок регистров специальных функций

| Символ | Наименование | Адрес |

| *ACC | Аккумулятор | 0E0H |

| * B | Регистр-расширитель аккумулятора | 0F0H |

| * PSW | Слово состояния программы | 0D0H |

| SP | Регистр-указатель стека | 81H |

| DPTR | Регистр-указатель данных (DPH) (DPL) | 83H |

| 82H | ||

| * P0 | Порт 0 | 80H |

| * P1 | Порт 1 | 90H |

| * P2 | Порт 2 | 0A0H |

| * P3 | Порт 3 | 0B0H |

| * IP | Регистр приоритетов | 0B8H |

| * IE | Регистр маски прерываний | 0A8H |

| TMOD | Регистр режима таймера/счетчика | 89H |

| * TCON | Регистр управления/статус таймера | 88H |

| TH0 | Таймер 0 (старший байт) | 8CH |

| TL0 | Таймер 0 (младший байт) | 8AH |

| TH1 | Таймер 1 (старший байт) | 8DH |

| TL1 | Таймер 1 (младший байт) | 8BH |

| * SCON | Регистр управления приемопередатчиком | 98H |

| SBUF | Буфер приемопередатчика | 99H |

| PCON | Регистр управления мощностью | 87H |

| Примечание. Регистры, имена которых отмечены знаком (*), допускают адресацию отдельных бит. |

При выполнении многих команд в АЛУ формируется ряд признаков операции (флагов), которые фиксируются в регистре ССП. В табл.3.2 приводится перечень флагов ССП, даются их символические имена и описываются условия их формирования.

Таблица 1.2 – Формат слова состояния программы (ССП)

| Символ | Позиция | Имя и назначение |

| C | PSW.7 | Флаг переноса. Устанавливается и сбрасывается аппаратурными средствами или программой при выполнении арифметических и логических операций |

| AC | PSW.6 | Флаг вспомогательного переноса. Устанавливается и сбрасывается только аппаратурными средствами при выполнении команд сложения и вычитания и сигнализирует о переносе или заем в бите 3 |

| F0 | PSW.5 | Флаг 0. Может быть установлен, сброшен или проверен программой как флаг, специфицируемый пользователем |

| RS1 RS0 | PSW.4 PSW.3 | Выбор банка регистров. Устанавливается и сбрасывается программой для выбора рабочего банка регистров (см. примечание) |

| OV | PSW.2 | Флаг переполнения. Устанавливается и сбрасывается аппаратно при выполнении арифметических операций |

| PSW.1 | Не используется | |

| P | PSW.0 | Флаг паритета. Устанавливается и сбрасывается аппаратуры в каждом цикле команды и фиксирует нечетное/четное число единичных бит в аккумуляторе, т.е. выполняет контроль по четности |

Наиболее "активным" флагом ССП является флаг переноса, которые принимает участие и модифицируется в процессе выполнения множеств операций, включая сложение, вычитание и сдвиги. Кроме того, флаг переноса (C) выполняет функции "булевого аккумулятора" в командах, манипулирующих с битами. Флаг переполнения (OV) фиксирует арифметическое переполнение при операциях над целыми числами со знаком и делает возможным использование арифметики в дополнительных кодах. АЛУ не управляет флагами селекции банка регистров (RS0, RS1), и их значение полностью определяется прикладной программой и используется для выбора одного из четырех регистровых банков.

Широкое распространение получило представление о том, что в микропроцессорах, архитектура которых опирается на аккумулятор, большинство команд работают с ним, используя адресацию "по умолчанию" (неявную). В МК51 дело обстоит иначе. Хотя процессор в МК51 имеет в своей основе аккумулятор, однако, он может выполнять множество команд и без участия аккумулятора. Многие логические операции могут быть выполнены без участия аккумулятора. Кроме того, переменные могут быть инкрементированы, декрементированы и проверены (test) без использования аккумулятора. Флаги и управляющие биты могут быть проверены и изменены аналогично.

1.5 Регистры-указатели

8-битный указатель стека (РУС) может адресовать любую область РПД. Его содержимое инкрементируется прежде, чем данные будут запомнены в стеке в ходе выполнения команд PUSH и CALL. Содержимое РУС декрементируется после выполнения команд POP и RET. В процессе инициализации МК51 после сигнала СБР в РУС автоматически загружается код 07H. Это значит, что если прикладная программа не переопределяет стек, то первый элемент данных в стеке будет располагаться в РПД по адресу 08Н.

Двухбайтный регистр-указатель данных (РУД) обычно используется для фиксации 16-битного адреса в операциях с обращением к внешней памяти. Командами МК51 регистр-указатель данных может быть использован или как 16-битный регистр, или как два независимых 8-битных регистра (DPH и DPL).

1.6 Таймер/счетчик

В составе средств МК51 имеются регистровые пары с символическими именами ТНО, TLO и THI, TLI, на основе которых функционируют два независимых программно-управляемых 16-битных таймера/счетчика событий.

Буфер последовательного порта. Регистр с символическим именем SBUF представляет собой два независимых регистра - буфер приемника и буфер передатчика. Загрузка байта в SBUF немедленно вызывает начало процесса передачи через последовательный порт. Когда байт считывается из SBUF, это значит, что его источником является приемник последовательного порта.

Регистры специальных функций. Регистры с символическими именами IP, IE, TMOD, TCON, SCON и PCON используются для фиксации и программного изменения управляющих бит и бит состояния схемы прерывания, таймера/счетчика, приемопередатчика последовательного порта и для управления мощностью электропитания МК51. Их организация будет описана ниже при рассмотрении особенностей работы МК51 в различных режимах.

1.7 Устройство управления и синхронизации

Кварцевый резонатор, подключаемый к внешним выводам X1 и X2 корпуса МК51, управляет работой внутреннего генератора, который в свою очередь формирует сигналы синхронизации.

Устройство управления МК51 на основе сигналов синхронизации формирует машинный цикл фиксированной длительности, равной 12 периодам резонатора или шести состояниям первичного управляющего автомата. Каждое состояние управляющего автомата содержит две фазы сигналов резонатора. Весь машинный цикл состоит из 12 фаз.

Большинство команд МК51 выполняется за один машинный цикл. Некоторые команды, оперирующие с 2-байтными словами или связанные с обращением к внешней памяти, выполняются за два машинных цикла. Только команды деления и умножения требуют четырех машинных циклов. На основе этих особенностей работы устройства управления МК51 производится расчет времени исполнения прикладных программ.

2 ПОСТАНОВКА ЗАДАЧ ПРОЕКТА

2.1 Требования к структуре и интерфейсу гипотетического микропроцессора

Разрабатываемый микропроцессор, дожжен иметь структуру и интерфейс, схожий с заданным микропроцессором-прототипом – МК51.

Разрабатываемый микропроцессор должен иметь в своем составе следующие структурные элементы:

1. арифметико-логическое устройство (АЛУ), предназначенное для выполнения группы арифметических и логических операций;

2. резидентную память программ (РПП), для хранения команд и адресов операндов;

3. резидентную память данных (РПД), для хранения исходных данных операций и результатов их выполнения;

4. устройство управления и синхронизации;

5. регистр адреса (РА), адресующий данные в РПД;

6. счетчик команд (СК), адресующий данные в РПП;

7. порты 0,1,2,3, для работы с внешней памятью программ и внешней памятью данных;

8. регистр указатель данных (РУД), для адресации данных во внешней памяти;

9. слово состояния программы (СПП), для хранения флагов работы программы;

10. шину, связывающую между собой основные узлы процессора.

Множество команд микропроцессора должно являться подмножеством команд микропроцессора МК51 и включать в себя команды трех основных типов: арифметико-логические, посылочные и команды переходов.

Группа команд арифметико-логического типа должна состоять из команд ADDC – сложение аккумулятора с байтом из регистра общего назначения, MUL – умножение аккумулятора на регистр B, RL – циклический сдвиг аккумулятора влево.

Группа команд посылочного типа должна состоять из команд MOV – пересылка в регистр прямоадресуемого байта, XCH – обмен аккумулятора с прямоадресуемым байтом.

Группа команд переходов должна состоять из команд LJMP – длинный переход в полном объеме памяти программ, JMP – косвенный относительный переход.

2.2 Требования к структуре АЛУ микропроцессора

Арифметико-логическое устройство (АЛУ), разрабатываемого микропроцессора должно иметь тип ЗМО и структуру, позволяющую ему выполнять заданный набор арифметико-логических операций (ADDC, MUL, RL, XCH).

В соответствии с этими требованиями, разрабатываемое АЛУ должно иметь в своем составе следующий набор структурных элементов:

1. накапливающий сумматор, для хранения одного из операндов и результата определенных операций;

2. два вспомогательных регистра, для хранения, в случае необходимости, второго операнда и хранения результата операции соответственно.

2.3 Требования к структуре микро ЭВМ

Структура, разрабатываемой микро ЭВМ должна отражать функциональные возможности системы команд, реализованной в микропроцессоре и иметь шинный интерфейс. С этой целью в микро ЭВМ должен быть введен следующий набор структурных элементов:

1. микропроцессор (МП);

2. генератор синхросигналов и начальных условий (ГСС и НУ);

3. внешняя память программ (ВПП);

4. внешняя память данных (ВПД);

5. блок обработки прерываний (БОП);

6. последовательный интерфейс для связи с внешними устройствами (ПИ).

3 РАЗРАБОТКА АРИФМЕТИКО-ЛОГИЧЕСКОГО УСТРОЙСТВА

В соответствии с заданием, арифметико-логическое устройство проектировалось как автомат с закрепленными микрооперациями, реализующий следующий набор команд ADDC – команда сложения аккумулятора с регистром общего назначения и переносом; MUL – команда умножения аккумулятора на регистр B; RL – команда циклического сдвига аккумулятора влево. Все операции в АЛУ выполняются над операндами, представленными в прямом коде.

3.1 Структурные схемы ОА операций

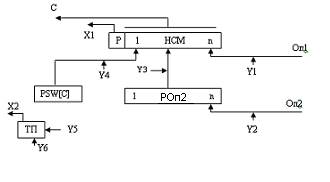

Операция ADDC – сложение аккумулятора с байтом из РПД и переносом. Структурная схема ОА для выполнения операции ADDC представлена на рисунке 3.1.

Рисунок 3.1 – Структурная схема ОА выполнения операции ADDC

Состав ОА выполнения операции ADDC:

1. НСМ – сумматор накапливающего типа(хранит первый операнд);

2. PОп2 – регистр(хранит второй операнд);

3. PSW[C] – флаг переноса;

4. ТП – триггер переполнения при выполнении операции.

Набор микроопераций:

y1: НСМ:=Оп1;

y2: PОп2:=Оп2;

y3: НСМ:=НСМ+PОп2;

y4: НСМ:=НСМ+PSW[C];

y5: ТП:=1;

y6: ТП:=0.

Осведомительные сигналы:

X1: НСМ[P];

X2: ТП.

Операция MUL – умножение аккумулятора на регистр B. Младший байт результата заноситься в аккумулятор, а старший в регистр B. Умножение выполняется по алгоритму A: множимое последовательно умножается на разряды множителя bn,…,b1 и добавляется на каждом шаге к сдвинутой вправо сумме частичных произведений. Структурная схема ОА для выполнения операции MUL представлена на рисунке 3.2.

Рисунок 3.2 – Структурная схема ОА выполнения операции MUL

Состав ОА выполнения операции MUL:

1. НСМ – сумматор накапливающего типа (хранит сумму частичных произведений);

2. РОп1 – регистр множителя;

3. РОп2 – регистр множимого;

4. СчТ – счетчик тактов.

Набор микроопераций:

Y1: РОп1:=Мт;

Y2: РОп2:=Мн;

Y3: НСМ:=НСМ+РОп2;

Y4: Рп1:=НСМ[n].R1(РМТ);

Y5: НСМ:=0.R1(НСМ);

Y6: СчТ:=n;

Y7: СчТ:=СчТ-1;

Y8: НСМ:=0.

Осведомительные сигналы:

X1: РМТ[n];

X2: СчТ=0.

Операция RL – циклический сдвиг аккумулятора влево. Структурная схема ОА для выполнения операции RL представлена на рисунке 3.3.

Набор микроопераций:

Y1: НСМ:=Оп;

Y2: Y3: НСМ:=L1(НСМ).НСМ[Р].

3.2 Разработка общего АЛУ.

Разрабатываемое АЛУ представляет собой ОА с закрепленными микрооперациями. Все операции в АЛУ выполняются над операндами, представленными в прямом коде. У всех операционных автоматов выноситься общая часть и объединяется с оставшимися частями.

Структурная схема ОА АЛУ представлена на рисунке 3.4.

Рисунок 3.4 – Структурная схема ОА АЛУ.

Рисунок 3.5 – Структурная схема ОА АЛУ.

Микрооперации:

Y1: НСМ:=Оп1;

Y2: РМН:=Оп2;

Y3: НСМ:=НСМ+РМН;

Y4: НСМ:=НСМ+PSW[C];

Y5: РМТ:=НСМ[n].R1(РМТ);

Y6: НСМ:=0.R1(НСМ);

Y7: НСМ:=L1(НСМ).НСМ[Р];

Y8: НСМ:=0;

Y9: РМТ:=Оп1;

Y10: СчТ:=n;

Y11: СчТ:=СчТ-1;

Y12: ТП:=1;

Y13: ТП:=0;

Y14: РМТ:=Оп2.

Осведомительные сигналы:

X1: НСМ[P];

X2:РМТ[n];

X3: ТП;

X4:СчТ=0.

3.3 Микропрограммы работы АЛУ

Алгоритм выполнения операции ADDC состоит в следующем. В сумматор (НСМ) заносится первое слагаемое, в регистр РМН – второе. Результат сложения записывается на место первого слагаемого, т.е. в сумматор. Затем значение флага переноса прибавляется к получившемуся результату и подается на выход.

Микропрограмма выполнения в АЛУ операции ADDC представлена на рисунке 3.5.

Рисунок 3.5 – Микропрограмма выполнения операции ADDC

Умножение выполняется по первому алгоритму: умножение с младших разрядов множителя со сдвигом суммы частичных произведений вправо. Старшая часть результата подается на выход Сст, а младшая на выход Смл. Микропрограмма выполнения операции MUL представлена на рисунке 3.6.

Рисунок 3.6 – Микропрограмма выполнения операции MUL

Операция RL – циклический сдвиг аккумулятора влево. Операнд записывается в НСМ. Над содержимым НСМ выполняется операция сдвига влево. Бит НСМ[1] переходит в бит НСМ[Р], который затем пересылается в бит НСМ[n]. Микропрограмма выполнения в АЛУ операции RL представлена на рисунке 3.7.

Рисунок 3.7 – Микропрограмма выполнения операции RL

Общая микропрограмма выполнения операций в АЛУ представлена на рисунке 3.8.

Рисунок 3.8 – Общая микропрограмма выполнения операций в АЛУ.

4 РАЗРАБОТКА СТРУКТУРЫМИКРОПРОЦЕССОРА

4.1 Система команд гипотетического микропроцессора

Система команд гипотетического микропроцессора включает семь команд: арифметические – ADDC, MUL(A); логические – RL; пересылки – MOV, XCH; перехода – LJMP, JMP.

Команда ADDC

Эта команда работает с двумя операндами и выполняет их арифметическое сложение, а так же сложение полученного результата с флагом переноса. Первый операнд, используемый в операции, хранится в аккумуляторе (АСС). Адрес второго операнда хранится в нулевом либо первом регистре общего назначения. Результат помещается в аккумулятор.

Формат команды: ADDC.

Код операции: 036h.

Команда MUL (А)

Эта команда работает с двумя операндами и выполняет их умножение по алгоритму А. Первый операнд храниться в аккумуляторе, второй операнд – в регистре B. Старший байт результата помещается в регистр В, младший – в аккумулятор.

Формат команды: MUL.

Код операции: 0A4h.

Команда RL

Эта команда работает с одним операндом и выполняет его циклический сдвиг влево. Операнд храниться в аккумуляторе. Результат записывается в аккумулятор.

Формат команды: RL.

Код операции: 023h.

Команда MOV

Эта команда работает с двумя операндами и выполняет пересылку второго операнда в первый. Первый операнд храниться в одном из регистров общего назначения. Адрес второго операнда указан в команде в качестве второго параметра.

Формат команды: MOV.

Код операции: 0А8h.

Команда XCH

Эта команда работает с двумя операндами и обменивает их местами. Первый операнд содержится в аккумуляторе, а адрес второго операнда указывается в команде в качестве второго аргумента.

Формат команды: XCH

Код операции: 0C5h.

Команда LJMP

Эта команда работает с одним операндом, и выполняет длинный переход в полном объеме памяти программ по адресу, указанному в качестве операнда.

Формат команды: LJMP.

Код операции: 02h.

Команда JMP

Эта команда работает с двумя операндами, и выполняет косвенный относительный переход. Результирующий адрес перехода вычисляется как сумма двух операндов. Первый операнд задан в аккумуляторе, а второй – в регистре управления данными (DPTR).

Формат команды: JMP.

Код операции: 073h.

4.2 Структура гипотетического микропроцессора

В связи с тем, что система команд гипотетического микропроцессора составляет 7 команд, его структурная схема значительно проще, чем структурная схема микропроцессора-прототипа. Многие элементы микропроцессора-прототипа не используются, в следствие чего они исключаются из исходной схемы. Получившаяся в результате упрощений структурная схема приведена на рисунке 4.1.

Рисунок 4.1 – Структурная схема гипотетического микропроцессора.

Разработанный процессор-прототип содержит следующие структурные элементы.

РПП – резидентная память программ предназначена для хранения команд, констант, управляющих слов инициализации, таблиц перекодировки входных и выходных сменных и т.п. РПП имеет 16-битную шину адреса, через которую обеспечивается доступ из счетчика команд или из регистра-указателя данных. Имеет емкость 4 килобайта.

РПД – резидентная память данных предназначена для хранения переменных в процессе выполнения прикладной программы, адресуется одним байтом и имеет емкость 128 байт.

АЛУ – арифметико-логическое устройство может выполнять арифметические операции сложения, деления и логическую операцию обмена местами тетрад в аккумуляторе;

Устройство синхронизации и управления – формирует сигналы синхронизации.

ССП – слово состояния программы –содержит ряд признаков операции (флагов), которые формируются при выполнении некоторых команд в АЛУ.

СК – счетчик команд, содержит адрес текущей команды.

РА – регистр адреса. Хранит адрес в РПД, по которому будет производиться операция чтения/записи

РУД – регистр указатель данных. Используется в операциях, связанных с чтением/записью во внешнюю память.

РК – регистр команд. Хранит код текущей операции и адреса операндов.

Порты (0 – 3) – порты ввода/вывода информации. Используются для доступа к внешней памяти данных (ВПД).

А – аккумулятор. Используется при арифметических операциях. Хранит первый операнд. Является местом фиксации результата выполнения арифметических и ряда логических операций.

4.3 Организация оперативного запоминающего устройства

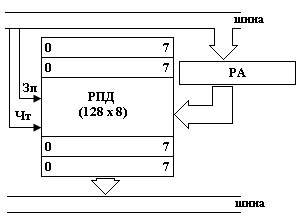

Одним из наиболее важных элементов, разрабатываемого микропроцессора, является, оперативное запоминающее устройство или резидентная память данных (РПД), предназначенное для временного хранения значений данных, используемых в операциях. Схема организации РПД представлена на рисунке 4.2.

Рисунок 4.2 – Схема организации резидентной памяти данных

Оперативное запоминающее устройство в разработанном процессоре имеет размер 128 байт.

Специальный регистр адреса (РА) позволяет адресовать любую ячейку в РПД и содержит адрес ячейки данных, которая будет прочитана или перезаписана.

Прочитанные данные, либо данные подлежащие записи помещаются в специальный регистр данных.

Установка ВПД в режим чтения или записи осуществляется путем посылки соответствующего сигнала записи или чтения.

4.4 Организация резидентной памяти программ.

Резидентная память программ (РПП) имеет емкость 4 килобайта и предназначена для хранения кодов команд, адресов операций, констант и т.д. РПП имеет 8-битную шину адреса, через которую обеспечивается доступ из счетчика команд (СК) или из регистра-указателя данных. Регистр-указатель данных выполняет функции базового регистра при косвенных переходах по программе или используется в операциях работы с внешней памятью данных и внешней памятью программ.

Схема организации РПП представлена на рисунке 4.3.

Рисунок 4.3 – Схема организации резидентной памяти программ

В отличие от оперативного запоминающего устройства (РПД) резидентная память программ не подлежит перезаписыванию. Для нее возможно выполнение лишь операции, связанной с чтением данных. Адрес данных в РПП, подлежащих прочтению хранится в счетчике команд (СК).

4.5 Структура регистра команд

Регистр команды (РК), используется при выполнении всех операций, осуществляемых, разрабатываемым микропроцессором. РК хранит двоичный код текущей операции, а так же адреса в резидентной памяти данных, принадлежащие операндам, используемым в операции.

Схема организации регистра команд, представлена на рисунке 4.4.

Рисунок 4.4 – Схема организации регистра команд

Регистр команд имеет размер три байта и состоит из следующих структурных частей:

1. КОП – восьмибитный регистр, хранящий код т