В отличие от комбинационных логических цепей триггеры - это логические устройства с памятью. Их выходные сигналы в общем случае зависят не только от сигналов, приложенных к входам в данный момент времени, но и от сигналов, воздействовавших на них ранее. В зависимости от свойств, числа и назначения входов триггеры можно разделить на несколько видов.

По способу приема информации триггеры подразделяют на тактируемые и не тактируемые триггеры. Изменение состояния на не тактируемого (асинхронного) триггера происходит сразу же после соответствующего изменения потенциалов на его управляющих входах.

В тактируемом (синхронном) триггере изменение состояния может произойти только в момент присутствия соответствующего сигнала на тактовом входе.

Тактирование может осуществляться импульсом (статическое управление) или фронтом/срезом (динамическое управление). В первом случае сигналы на управляющих входах оказывают влияние на состояние триггера только при разрешающем потенциале на тактовом входе. Во втором случае воздействие управляющих сигналов проявляется только в момент перехода единица - нуль или нуль - единица на тактовом входе.

Существуют также универсальные триггеры, которые могут работать как в тактируемом, так и в не тактируемом режиме.

Основные типы триггеров в интегральном исполнении носят следующие названия: D -триггеры, Т -триггеры, RS -триггеры и JK -триггеры.

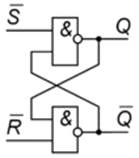

В зависимости от логической структуры различают RS -триггеры с прямыми и инверсными входами. Их схемы приведены на рис. 55. Триггеры такого типа построены на двух логических элементах «2ИЛИ-НЕ» - триггер с прямыми входами (активный уровень лог. 1), «2И-НЕ» - триггер с инверсными входами (активный уровень лог.0). В данном случае изображены потенциальные асинхронные триггера, Потенциальный означает, что триггер срабатывает от уровня сигнала, а асинхронный – момент срабатывания произвольный и зависит от входных сигналов. Входа R и S называются информационными.

Рис. 55. Структуры RS-триггера

Принцип работы:

1. Чтобы записать на выход триггера Q лог. 1 необходимо на вход S подать активный уровень, а на R – пассивный.

2. Чтобы записать на выход триггера Q лог. 0 необходимо на вход S подать пассивный уровень, а на R – активный.

3. Если необходимо сохранять состояние триггера, то на S и R подаются пассивные уровни.

4. Два активных уровня на входах триггера переводят его в запрещенное состояние.

Исходя из вышесказанного таблица состояний для RS -триггера, собранного на «2ИЛИ-НЕ» имеет следующий вид:

Таблица состояний для RS -триггера, собранного на «2ИЛИ-НЕ»

| Такт tn | Такт tn+1 | |

| R | S | Qn+1 |

| Qn | ||

| запрещенное |

Таблица для RS -триггера, собранного на «2И-НЕ»:

Таблица состояний для RS -триггера, собранного на «И-НЕ»

| Такт tn | Такт tn+1 | |

| R | S | Qn+1 |

| запрещенное | ||

| Qn |

Рассмотрим работу триггера на элементах «2ИЛИ-НЕ».

Пусть в исходном состоянии на выходе Q триггера лог. 0, а на  - лог. 1. Необходимо переключить триггер в состояние при котором на Q будет лог. 1, а на

- лог. 1. Необходимо переключить триггер в состояние при котором на Q будет лог. 1, а на  соответственно лог. 0. Согласно таблице состояний данного триггера, необходимо подать на вход S лог. 1, а на вход R лог. 0. В результате на выходе нижнего элемента «2ИЛИ-НЕ» формируется лог. 0 (выход

соответственно лог. 0. Согласно таблице состояний данного триггера, необходимо подать на вход S лог. 1, а на вход R лог. 0. В результате на выходе нижнего элемента «2ИЛИ-НЕ» формируется лог. 0 (выход  ), который поступает на второй вход верхнего логического элемента по цепи обратной связи, в результате на выход логического элемента формируется лог.1 (выход Q). В результате видим, что триггер переключился в заданное нами состояние.

), который поступает на второй вход верхнего логического элемента по цепи обратной связи, в результате на выход логического элемента формируется лог.1 (выход Q). В результате видим, что триггер переключился в заданное нами состояние.

По аналогии можно проанализировать остальные состояния триггера.

На рис. 56 приведены временные диаграммы работы RS -триггера с прямыми входами.

Рис. 56. Диаграммы работы RS -триггера с прямыми входами

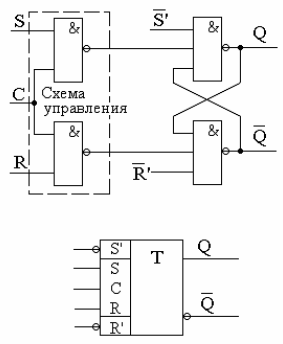

На рис. 57 приведена структура и условное обозначение RS-триггеров со статическим управлением.

Рис. 57. RS -триггер со статическим управлением

Особенностью синхронных RS -триггеров, представленных на рис. 57, является применение в схеме управления инвертирующих («ИЛИ-НЕ», «И-НЕ»), приводящее к изменению исполнительных значений управляющих сигналов по сравнению с асинхронными RS -триггерами, собранными на аналогичных ИЛЭ.

Рассмотрим таблицы состояний для каждой структуры.

Таблица для структуры №1:

| Такт tn | Такт tn+1 | ||

| C | R | S | Qn+1 |

| Qn | |||

| Qn | |||

| Qn | |||

| Qn | |||

| Qn | |||

| запрещенное |

Таблица для структуры №2:

| Такт tn | Такт tn+1 | ||

| C | R | S | Qn+1 |

| Qn | |||

| Qn | |||

| Qn | |||

| Qn | |||

| Qn | |||

| запрещенное |

На рис. 58 приведена структура RS -триггера с приоритетными входами. Они получили такое название благодаря тому, что они позволяют устанавливать триггер в определенное состояние перед началом работы.

Рис. 58. RS -триггер со статическим управлением и приоритетными

входами

На рис. 59 приведены структура и условное обозначение RS -триггеров с активным уровнем лог. 0.

Рис. 59. RS -триггер со статическим управлением и приоритетными

входами (активный уровень лог. 0)

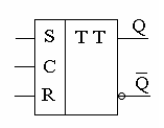

Рассмотренные RS -триггеры реагируют на исполнительное значение входных информационных сигналов сразу же после их подачи, т.е. по переднему фронту сигналов (в синхронных триггерах – с появлением синхроимпульсов). Такие триггеры называются одноступенчатыми и имеют на условном обозначении в основном поле одну букву Т. Одноступенчатые триггеры не могут быть использованы для построения нашедших широкое применение в цифровой технике однотактных регистров и счетчиков, в которых триггеры соединяются последовательно друг с другом.

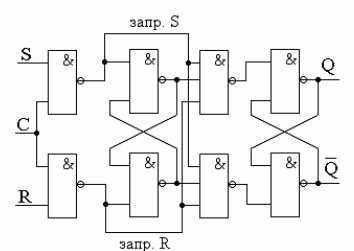

Для решения этой задачи применяются двухступенчатые триггеры. Двухступенчатые триггеры состоят из двух триггеров первой и второй степени. Триггер первой ступени предназначен для приема (записи) информации и передачи ее в триггер второй ступени в промежутке между тактовыми импульсами. На рис. 60 приведена структура такого триггера.

Рис. 60. Структура двухступенчатого триггера

Внутренние связи между триггерами первой и второй ступени обеспечивают следующий порядок работы в каждом такте:

- запись входной информации в запоминающий триггер первой ступени с одновременным блокированием входов триггера второй ступени и сохранением его исходного состояния;

- блокирование входов триггера первой ступени с одновременной перезаписью информации из нее в разблокированную вторую ступень.

Осуществлять управление двухступенчатым триггером одной тактовой последовательностью синхроимпульсов можно, если между синхроимпульсов первой и второй ступеней включить инвертор.

В этой схеме при поступлении синхроимпульса С = 1первая ступень будет разблокирована, а вторая заблокирована, т.к. на ее входе действует синхросигнал С = 0. После окончания синхроимпульса вторая ступень окажется разблокированной и информация, записанная в первой ступени, перепишется в нее. Так как информация в двухступенчатом триггере снимается с выхода триггера второй ступени, то, в отличие от одноступенчатых, двуступенчатые триггеры срабатывают после спада синхроимпульса (срез импульса), т.е. в них осуществляется задержка опрокидывания на время, равное длительности синхроимпульса. Условное графическое обозначение двухступенчатого RS -триггера приведено на рис. 61.

Рис. 61. Условное графическое обозначение двухступенчатого RS -триггера

Еще один вариант двухступенчатого триггера приведен на рис. 62.

Рис. 62. Второй вариант двухступенчатого триггера

8. JK -триггеры. Логические структуры триггеров, таблицы