Логическими элементами (ЛЭ) называются функциональные устройства, с помощью которых реализуются элементарные логические функции. Даже самые сложные преобразования цифровой информации, в конечном счете, сводятся к простейшим операциям над логическими переменными 0 и 1. Такие операции реализуются ЛЭ в соответствии с формулами алгебры логики.

В реальных условиях логические переменные 0 и 1 отображаются, как правило, двумя различными уровнями напряжения: U0 и U1. Переход от логических переменных к электрическим сигналам ставит вопрос о логических соглашениях. Существуют соглашения положительной и отрицательной логики. В положительной логике U1 > U0, а в отрицательной U1 < U0. Один и тот же элемент, в зависимости от принятого логического соглашения, выполняет различные логические операции. Переход от операции в положительной логике к операции в отрицательной производится инвертированием всех переменных. В дальнейшем рассмотрении свойств схем будем пользоваться соглашением положительной логики.

По виду схемотехнической реализации основных логических операций и принципу построения базовых ЛЭ различают следующие типы интегральных логических схем:

- транзистор-транзисторные (ТТЛ, ТТЛШ);

- транзисторные с эмиттерными связями между элементами (ЭСЛ);

- транзисторная логика на МДП-транзисторах (КМОП).

"Естественный отбор" среди различных схем ЛЭ привел к тому, что в настоящее время в схемотехнологии КМОП и ТТЛШ стали основными. В каждом типе можно выделить базовый ЛЭ И-НЕ или ИЛИ-НЕ, а его модификации служат для упрощения структур устройств, построенных на его основе.

Элемент И-НЕ осуществляет логическую операцию умножения сигналов (логических переменных) Х1, Х2… с инверсией результата:  . Условное графическое изображение двухвходового элемента И-НЕ и его таблица состояний приведены на рис.1.1.

. Условное графическое изображение двухвходового элемента И-НЕ и его таблица состояний приведены на рис.1.1.

| Х1 | Х2 | Y |

Рис. 1.1. Схемное обозначение элемента И-НЕ и его таблица состояний

Это означает, что выходной сигнал Y = 0 тогда и только тогда, когда Х1 = Х2 = 1. Если хотя бы одна из переменных будет равна 0, то Y = 1.

Элемент ИЛИ-НЕ осуществляет сложение логических сигналов с инверсией результата:  , т.е. Y = 0, если хотя бы один из входов равен 1, и Y = 1, если все входы равны 0. Условное графическое изображение двухвходового элемента ИЛИ-НЕ и его таблица состояний приведены на рис.1.2.

, т.е. Y = 0, если хотя бы один из входов равен 1, и Y = 1, если все входы равны 0. Условное графическое изображение двухвходового элемента ИЛИ-НЕ и его таблица состояний приведены на рис.1.2.

| Х1 | Х2 | Y |

Рис.1.2. Схемное обозначение элемента ИЛИ-НЕ и его таблица состояний

Таким образом, если сигналы 0 считать единицами, а 1 – нулями, то И-НЕ станет ИЛИ-НЕ, и наоборот.

Параметры ЛЭ. Основными параметрами, характеризующими ЛЭ, являются следующие группы:

- функциональные, определяющие логические возможности при применении микросхем в аппаратуре;

- измеряемые, являющиеся измеряемыми физическими величинами, через которые выражаются функциональные параметры.

К функциональным параметрам относятся:

- реализуемая логическая функция;

- коэффициент разветвления по выходу Краз, определяющий максимально допустимое число единичных нагрузок, которые можно одновременно подключить к выходу микросхемы. Единичной нагрузкой или эталонной нагрузочной ячейкой считается один вход аналогичного элемента, входящего в заданный набор;

- коэффициент объединения по входу Коб, характеризующий максимально допустимое число входов, по которым реализуется логическая функция;

- помехоустойчивость Uпом, определяемая максимально допустимым напряжением статической помехи на входе интегральной схемы, при котором еще не происходит изменение уровней ее выходного потенциала;

- потребляемая мощность Рпот, представляющая собой мощность, потребляемую ИС от источника питания в заданном режиме. Различают мощности Р1пот и Р0пот, потребляемые ИС в состояниях логических 1 и 0, а также среднюю потребляемую мощность Рпот.ср.=0.5(Р1пот + Р0пот).

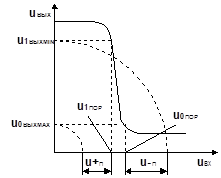

Измеряемые параметры, включают в себя статические и динамические характеристики и параметры. К статическим параметрам относятся значения входных и выходных токов логических 1 и 0, выходных напряжений логических 1 и 0, пороговых напряжений логических 1 и 0, токи, потребляемые ИС в двух состояниях. Статические свойства схемы наглядно отражает передаточная характеристика, представляющая собой зависимость напряжения на выходе ИС от напряжения на одном из входов: Uвых = f(Uвх), приведенная на рис.1.3.

На графике этой зависимости проводят уровни U1выхmin и U0выхmax. Напряжение U1выхmin равно минимальному значению уровня логической 1 на выходе схемы. Сигнал Uвых > U1выхmin считают единичным. Напряжение U0выхmax соответствует максимальному значению уровня логического 0 на выходе схемы. Сигнал Uвых < U0выхmax считается нулевым.

Рис.1.3. Передаточная характеристика ЛЭ

При Uвх < U1пор на выходе схемы поддерживается уровень логической 1. При Uвх > U0пор на выходе схемы поддерживается уровень логического 0. Универсальные ЛЭ делают взаимно согласованными так, чтобы уровни выходных сигналов одного ЛЭ могли использовать в качестве уровней входного сигнала аналогичного следующего элемента без каких-либо согласующих устройств. Такое согласование обеспечивается при U0выхmax £ U1пор, U1выхmin ³ U0пор. Эти неравенства выполняют с некоторым запасом.

При наличии на выходе предыдущей схемы напряжения U0вых £ U0выхmax это напряжение воспринимается последующей логической схемой как уровень логического 0 на входе. Так как U0выхmax < U1пор, то допускаются некоторые паразитные (помеховые) изменения входного сигнала, которые не приводят к изменению выходных сигналов последующей схемы.

Статическую помехоустойчивость ЛЭ характеризуют параметрами U+п и U-п. Напряжение U+п = U1пор - U0выхmax характеризует помехоустойчивость схемы к помеховым выбросам положительной полярности. Появление на входе схемы помехи Uп < U+п, добавляющейся к входному сигналу Uвх < U1пор еще не приводит к переключению выходного сигнала с уровня логической 1 на уровень логического 0. Аналогично, U-п = U0выхmax - U0пор характеризует помехоустойчивость схемы к отрицательным изменениям напряжения. При Uп < U-п ложное срабатывание схемы исключается.

Рис.1.4. Диаграмма переключения ИС

Динамические параметры логических ИС можно проиллюстрировать с помощью временных диаграмм входного и выходного напряжений при переключении микросхемы (рис.1.4). На временных диаграммах введены следующие обозначения: tзд0,1 - время переключения из состояния логического нуля в состояние логической единицы, измеренное между уровнями 0.1 и 0.9 логического перепада сигнала; tзд1,0 - время перехода из состояния логической единицы в состояние логического нуля, измеренное между уровнями 0.9 и 0.1 логического перепада сигнала; tзд.р1,0 - время задержки распространения сигнала при включении микросхемы, измеренное между уровнями 0.5 логического перепада входного и выходного сигналов; tзд.р0,1 - время задержки распространения сигнала при выключении микросхемы, измеренное между уровнями 0.5 логического перепада входного и выходного сигналов. Среднее время задержки распространения сигнала tзд.р.ср = (tзд.р1,0 + tзд.р0,1)/2.

2. Типы интегральных схем по виду схемотехнической реализации основных логических операций и принципу построения базовых ЛЭ.

3. Основные функциональные и измеряемые параметры, характеризующие ЛЭ.

4. Работа схемы ТТЛШ ЛЭ реализующего логическую функцию И-НЕ.

5. Работа схемы КМОП ЛЭ, реализующего логическую функцию ИЛИ-НЕ.

6. Работа схемы КМОП ЛЭ, реализующего логическую функцию И-НЕ.

7. Работа схемы КМОП ЛЭ, реализующего логическую функцию простого инвертора (НЕ).

8. Типы выходов ЛЭ. Выходной КМОП каскад с третьим состоянием.

9. Типы выходов ЛЭ. Выходной каскад ЛЭ с открытым коллектором или стоком.

10. Выходные каскады с возможностью их программирования TC – OC.

11. Общая характеристика функциональных узлов комбинационного типа. Основные типовые схемы комбинационного типа.

12. Шифратор. Функциональное назначение. Условно-графическое обозначение.

13. Дешифратор. Функциональное назначение. Условно-графическое обозначение.

14. Описание схемы двухвходового дешифратора в виде таблицы и системы уравнений.

15. Мультиплексор. Функциональное назначение. Условно-графическое обозначение.

16. Построение мультиплексора с двумя информационными входами X 1 ¸ X 2 и одним адресным A.

17. Построение мультиплексора с четырьмя информационными входами X 1 ¸ X 4 и двумя адресными A 1 и A 2.

18. Универсальные логические модули на основе мультиплексоров. Пример построения.

19. Демультиплексор. Функциональное назначение. Условно-графическое обозначение.

20. Сумматоры. Функциональное назначение. Таблица истинности и схема полного сумматора. Условно-графическое обозначение.

21. Параллельный сумматор с последовательным переносом для сложения двух многоразрядных двоичных чисел.

22. Параллельный сумматор с параллельным переносом для сложения двух многоразрядных двоичных чисел. Схема ускоренного (параллельного) переноса.

23. Арифметико-логические устройства (АЛУ). Функциональное назначение. Условно-графическое обозначение. Схемы наращивания АЛУ.

24. Общая характеристика функциональных узлов последовательностного типа.

25. Функциональное назначение и способы задания триггеров.

26. Общие классификационные признаки триггеров

27. Схемотехника триггерных устройств.

28. Схема асинхронного RS -триггера на элементах ИЛИ-НЕ.

29. Схема асинхронного RS -триггера на элементах И-НЕ.

30. Схема синхронного RS -триггера на четырех элементах И-НЕ.

31. Двухступенчатые триггеры.

32. Особенности построения JK -триггеров.

33. Синхронный D -триггер. Особенности функционирования.

34. Стандартный синхронный D -триггер. Особенности функционирования. Назначения выводов.

34. Стандартный синхронный JK -триггер. Особенности функционирования. Назначения выводов.

35. T -триггеры. Особенности функционирования. Назначение.

36. Параллельные регистры. Особенности построения параллельных регистров. Назначение.

37. Последовательные (сдвигающие) регистры. Особенности работы схемы сдвигового регистра на D -триггерах.

38. Функции, выполняемые универсальными реверсивными сдвигающими регистрами.

39. Счетчики. Классификация счетчиков. Основные характеристики. Применение счетчиков.

40. Схема и временные диаграммы работы двоичного, асинхронного суммирующего счетчика на T -триггерах.

41. Схема и временные диаграммы работы двоичного, асинхронного вычитающего счетчика на T -триггерах.

42. Схема и временные диаграммы работы двоичного, асинхронного реверсивного счетчика на T -триггерах.

43. Схема двоичного параллельного (синхронного) суммирующего счетчика.

44. Схема двоичного параллельного (синхронного) суммирующего счетчика.

45. Пример построения двоично-десятичного счетчика на основе микросхемы К155ИЕ5.

46. Запоминающие устройства. Общие сведения. Параметры запоминающих устройств. Типовые выводы микросхем памяти.

47. Параметры ЗУ, характеризующие его быстродействие. Временные диаграммы сигналов ЗУ при выполнении операций чтения и записи.

48. Адресные и последовательные способы доступа к данным ЗУ.

49. Постоянные запоминающие устройства. Назначение. Классификация.

50. Запоминающие элементы статических ОЗУ.

51. Запоминающие элементы динамических ОЗУ.

52. Память с последовательным доступом. Принцип построения памяти типа LIFO.

53. Память с последовательным доступом. Принцип построения памяти типа FIFO.

54. Назначение кэш-памяти. Структура кэш-памяти.