Цель работы: изучение сумматора, способов его проектирования, построение логических схем параллельного сумматора в булевом базисе, базисах Пирса и Шеффера, а также написание программы, описывающей работу сумматора, на языке VHDL.

Краткие теоретические сведения. Сумматоры выполняют арифметическое сложение и вычитание чисел. Имеют самостоятельное значение и являются также ядром схем арифметико-логических устройств (АЛУ), реализующих ряд разнообразных операций и являющихся непременной частью всех процессоров и спецвычислителей.

Аппаратная сложность и быстродействие сумматора являются очень важными параметрами и поэтому разработано множество вариантов сумматоров. Среди них можно выделить следующие типы сумматоров:

– одноразрядный сумматор без входного переноса;

– одноразрядный сумматор со входным переносом;

– многоразрядный последовательный сумматор с последовательным переносом;

– многоразрядный последовательный сумматор с параллельным переносом;

– многоразрядный параллельный сумматор.

Одноразрядный сумматор без входного переноса

Одноразрядный сумматор без входного переноса (рис. 3.1, а) имеет два входа (два слагаемых –  и

и  ) и 2 выхода (суммы

) и 2 выхода (суммы  и переноса

и переноса  в следующий разряд). Таблица истинности одноразрядного сумматора без входного переноса показана в табл. 3.1.

в следующий разряд). Таблица истинности одноразрядного сумматора без входного переноса показана в табл. 3.1.

Рис. 3.1. Одноразрядный сумматор: без входного переноса (а), со входным переносом (б)

Таблица 3.1. Таблица истинности одноразрядного сумматора без входного переноса

| № набора | Входы | Выходы | ||

|

|

|

| |

Одноразрядный сумматор без входного переноса реализует следующую функциональную зависимость:

.

.

Одноразрядный сумматор со входным переносом

Одноразрядный сумматор со входным переносом (см. рис. 3.1, б) имеет 3 входа (два слагаемых  и

и  , и перенос из предыдущего разряда

, и перенос из предыдущего разряда  ) и 2 выхода (суммы

) и 2 выхода (суммы  и переноса

и переноса  в следующий разряд).Таблица истинности одноразрядного сумматора со входным переносом показана в табл. 3.2.

в следующий разряд).Таблица истинности одноразрядного сумматора со входным переносом показана в табл. 3.2.

Таблица 3.2. Таблица истинности одноразрядного сумматора со входным переносом

| № набора | Входы | Выходы | |||

|

|

|

|

| |

Одноразрядный сумматор со входным переносом реализует операцию:

.

.

Многоразрядный последовательный сумматор с последовательным переносом

Многоразрядный последовательный сумматор с последовательным переносом (рис. 3.2) строится как цепочка одноразрядных сумматоров со входным переносом (см. рис. 3.1, б), соединенных последовательно по цепям переноса.

Рис. 3.2. Многоразрядный последовательный сумматор с последовательным переносом

Многоразрядный последовательный сумматор с параллельным переносом

Сумматоры с параллельным переносом разработаны для получения максимального быстродействия.

Сумматоры с параллельным переносом не имеют последовательного распространения переноса вдоль разрядной сетки. Во всех разрядах результаты вырабатываются одновременно, параллельно во времени. Сигналы переноса для данного разряда формируются специальными схемами, на входы которых поступают все переменные, необходимые для выработки переноса, т.е. те, от которых зависит его наличие или отсутствие. Такие схемы называют схемами ускоренного переноса. Сумматор на основе схемы (логики) ускоренного переноса, использующийся в ПЛИС серий Virtex и Spartan фирмы Xilinx показан на рис. 3.3. Аналогичным образом строится и сумматор-вычитатель на основе логики ускоренного переноса (рис. 3.4), у которого входной сигнал add = 1 при сложении, add = 0 – при вычитании.

Рис. 3.3. Многоразрядный последовательный сумматор на основе логики ускоренного переноса

Рис. 3.4. Многоразрядный последовательный сумматор-вычитатель на основе логики ускоренного переноса

Многоразрядный параллельный сумматор

‑разрядный параллельный сумматор без входного переноса имеет 2 входа:

‑разрядный параллельный сумматор без входного переноса имеет 2 входа:  и

и  . Такой сумматор имеет следующие выходные сигналы: сумма

. Такой сумматор имеет следующие выходные сигналы: сумма  и выходной перенос

и выходной перенос  . Его работа описывается выражением:

. Его работа описывается выражением:

, (3.1)

, (3.1)

где  ,

,  – двоичные разряды слагаемых,

– двоичные разряды слагаемых,  – двоичный разряд суммы,

– двоичный разряд суммы,  – разряд выходного переноса.

– разряд выходного переноса.

‑разрядный параллельный сумматор со входным переносом имеет 3 входа: два слагаемых

‑разрядный параллельный сумматор со входным переносом имеет 3 входа: два слагаемых  и

и  , а также входной перенос

, а также входной перенос  . Такой сумматор имеет следующие выходные сигналы: сумма

. Такой сумматор имеет следующие выходные сигналы: сумма  и выходной перенос

и выходной перенос  . Его работа описывается выражением:

. Его работа описывается выражением:

. (3.2)

. (3.2)

‑разрядный параллельный вычитатель без входного заема имеет 2 входа: уменьшаемое

‑разрядный параллельный вычитатель без входного заема имеет 2 входа: уменьшаемое  и вычитаемое

и вычитаемое  . Такой вычитатель имеет следующие выходные сигналы: разность

. Такой вычитатель имеет следующие выходные сигналы: разность  и выходной заем

и выходной заем  . Его работа описывается выражением:

. Его работа описывается выражением:

(3.3)

(3.3)

Исходные данные: приведены в табл. 3.3.

Таблица 3.3. Варианты заданий для построения 2‑разрядного параллельного сумматора/вычитателя

| № варианта | Операция | Наличие входного переноса | Вид минимальной формы | Тип конечного базиса |

| 1, 9 | Сумматор | да | МДНФ | Пирса |

| 2, 10 | Сумматор | да | МДНФ | Шеффера |

| 3, 11 | Сумматор | да | МКНФ | Пирса |

| 4, 12 | Сумматор | да | МКНФ | Шеффера |

| 5, 13, 17 | Вычитатель | нет | МДНФ | Пирса |

| 6, 14, 18 | Вычитатель | нет | МДНФ | Шеффера |

| 7, 15, 19 | Вычитатель | нет | МКНФ | Пирса |

| 8, 16, 20 | Вычитатель | нет | МКНФ | Шеффера |

Подготовка к работе: перед выполнением работы изучить теоретический материал по литературе и лекциям, выполнить пункты 1 – 8 задания для получения допуска к выполнению лабораторной работы.

Задание:

1) построить таблицу истинности 2‑разрядного параллельного сумматора/вычитателя;

2) найти СовДНФ или СовКНФ ПФ 2‑разрядного параллельного сумматора/вычитателя по его таблице истинности;

3) с помощью карт Карно найти МДНФ или МКНФ ПФ 2‑разрядного параллельного сумматора/вычитателя;

4) перейти от МДНФ или МКНФ ПФ 2‑разрядного параллельного сумматора/вычитателя к базису Пирса или Шеффера;

5) построить в универсальном базисе логическую схему 2‑разрядного параллельного сумматора/вычитателя для его ПФ, заданных в виде МДНФ или МКНФ.

6) построить в базисе Пирса или Шеффера логическую схему 2‑разрядного параллельного сумматора/вычитателя.

7) построить временные диаграммы работы 2‑разрядного параллельного сумматора/вычитателя;

8) написать программу на языке VHDL, реализующую 2‑разрядный параллельный сумматор/вычитатель в базисе Пирса или Шеффера;

9) провести моделирование 2‑разрядный параллельного сумматора/вычитателя в HDL Bencher;

10) получить конфигурационную последовательность проекта, реализующего 2‑разрядный параллельный сумматор/вычитатель для конкретной микросхемы ПЛИС и посмотреть ее в редакторе связей Floorplanner.

Содержание отчета:

1) название, цель работы, задание;

2) проектирование схемы в соответствии с планом задания (п.п. 1 – 8 задания);

3) результаты моделирования схемы 2‑разрядного параллельного сумматора/вычитателя в HDL Bencher.

Пример выполнения работы.

Исходные данные: параллельный 2‑разрядный сумматор без входного переноса, вид минимальной формы – МДНФ, тип конечного базиса – Пирса.

1‑й этап. Построение таблицы истинности для ПФ параллельный 2‑разрядный сумматор без входного переноса (табл. 3.4).

Таблица 3.4. Таблица истинности для ПФ параллельного 2‑разрядного сумматора без входного переноса

| № набора | Входы | Выходы | |||||

|

|

|

|

|

|

| |

2‑й этап. Нахождение СовДНФ и ПФ сумматора по таблице истинности (см. табл. 3.4).

3‑й этап. Нахождение МДНФ ПФ сумматора с помощью карт Карно:

, (3.4)

, (3.4)

, (3.5)

, (3.5)

. (3.6)

. (3.6)

4‑й этап. Переход от МДНФ ПФ сумматора к базису Пирса:

, (3.7)

, (3.7)

,(3.8)

,(3.8)

. (3.9)

. (3.9)

5‑й и 6‑й этапы. Построение ЛС параллельного сумматора в универсальном базисе (для ПФ (3.4) – (3.6)) и базисе Пирса (для ПФ (3.7) – (3.9)) (рис. 3.5).

Рис. 3.5. ЛС 2‑разрядного параллельного сумматора без входного переноса в базисе Пирса

7‑й этап. Построение временных диаграмм ЛС параллельного сумматора (рис. 3.6).

8‑й этап. Написание программы на языке VHDL, реализующей 2‑разрядный параллельный сумматор в базисе Пирса.

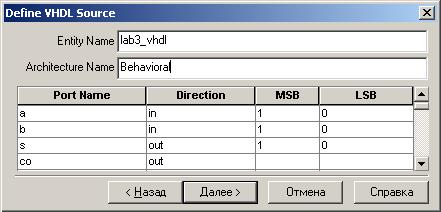

Диалоговое окно задания входных и выходных сигналов 2‑разрядного параллельного сумматора без входного переноса показано на рис. 3.7.

Программа на VHDL, реализующая 2‑разрядный параллельный сумматор в базисе Пирса, приняла вид:

library IEEE; -- Раздел описания библиотек

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity lab3_vhdl is -- Раздел объявления входных и выходных сигналов

Port (a: in std_logic_vector(1 downto 0);

b: in std_logic_vector(1 downto 0);

s: out std_logic_vector(1 downto 0);

co: out std_logic);

end lab3_vhdl;

architecture Behavioral of lab3_vhdl is -- описание сумматора в базисе Пирса

begin

s(0) <= not ((not ((not a(0)) or b(0))) or

(not (a(0) or (not b(0)))));

s(1) <= (not ((not (a(1) or a(0) or (not b(1)))) or

(not (a(1) or (not a(0)) or (not b(0)))) or

(not ((not a(0)) or (not b(1)) or (not b(0)))) or

(not ((not a(1)) or b(1) or b(0))) or

(not ((not a(1)) or a(0) or b(1)))));

co <= (not ((not ((not a(1)) or (not b(1)))) or

(not ((not a(0)) or (not b(1)) or (not b(0)))) or

(not ((not a(1)) or (not a(0)) or (not b(0))))));

end Behavioral; -- конец программы

Рис. 3.6. Временные диаграммы работы 2‑разрядного параллельного сумматора без входного переноса

Рис. 3.7. Диалоговое окно задания входных/выходных сигналов сумматора

9‑й этап. Моделирование 2‑разрядного параллельного сумматора без входного переноса в HDL Bencher (рис. 3.8).

Рис. 3.9. Результаты моделирования 2‑разрядного сумматора без входного переноса

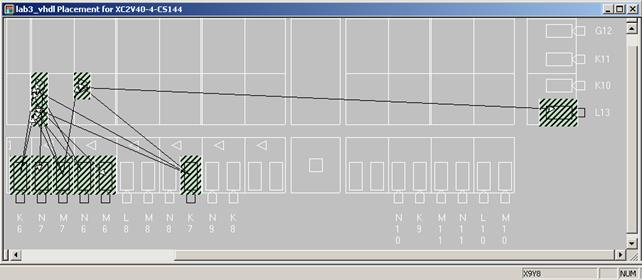

10‑й этап. Получение конфигурационной последовательности 2‑разрядного параллельного сумматора без входного переноса для конкретной микросхемы ПЛИС и просмотр размещения проекта внутри микросхемы в редакторе связей Floorplanner (рис. 3.9).

На рис. 3.9 показано 3 функциональных генератора, 4 входные ножки (K6, M7, N6 и K7) и 2 выходные (N7 и M6).

Рис. 3.9. Результаты размещения 2‑разрядного параллельного сумматора без входного переноса в микросхеме XC2V40-4-CS144

Контрольные вопросы:

1. Назначение сумматоров.

2. Типы сумматоров.

3. Одноразрядный сумматор без входного переноса (таблица истинности; ЛС в виде СовДНФ, СовКНФ, МДНФ, МКНФ; в базисе Пирса и Шеффера).

4. Одноразрядный сумматор со входным переносом (таблица истинности; ЛС в виде СовДНФ, СовКНФ, МДНФ, МКНФ; в базисе Пирса и Шеффера).

5. Многоразрядный последовательный сумматор с последовательным переносом (схема, принципы работы).

6. Многоразрядный последовательный сумматор с параллельным переносом (схема, принципы работы).

7. Многоразрядный параллельный сумматор (принципы работы).

8. Построить таблицу истинности параллельного 2‑разрядного сумматора/вычитателя.

9. Найти МДНФ и МКНФ параллельного 2‑разрядного сумматора/вычитателя.

10. Построить ЛС параллельного 2‑разрядного сумматора/вычитателя в булевом базисе, в базисах Пирса и Шеффера.

ЛАБОРАТОРНАЯ РАБОТА № 4